Oscillator如何在PCB上驅(qū)動多個負載

來源:http://www.benpai.com.cn 作者:金洛鑫電子 2019年08月17

驅(qū)動多個負載

PCB上的兩個或更多Oscillator可能需要相同頻率的輸入時鐘.使用時鐘驅(qū)動多個負載的一種方法是使用扇出緩沖器,這需要額外的電路板空間和功率.另一種方法是將一個輸出連接到多個負載.將一個輸出連接到多個負載的首選方法是將單個傳輸線路由到盡可能靠近負載,并使用星形連接將負載連接到短路徑,因此負載在路徑末端被認為是集總的.該方法要求負載彼此足夠接近.

如果負載彼此相距太遠而無法使用集總負載配置,那么在某些條件下,可以使用一個輸出來驅(qū)動兩條輸電線路分離負載.這種配置要求輸出驅(qū)動器具有比驅(qū)動單條傳輸線更高的電流驅(qū)動能力,當使用60Ω和更低阻抗的傳輸線時,不建議將其與1.8V版本的SiT1602和表2中列出的其他器件一起使用.在將此配置合并到設計中之前,建議使用IBIS模型運行信號完整性仿真.

某些驅(qū)動程序可能沒有足夠的驅(qū)動能力來處理兩條傳輸線.如果振蕩器輸出和負載之間的距離足夠小,則可以考慮星形拓撲.典型石英晶體振蕩器的輸出驅(qū)動器強度不足以驅(qū)動三條或更多條傳輸線,并且可以在PCB(50-60Ω)上輕松設計走線阻抗.SiTime晶振不建議從單個驅(qū)動器驅(qū)動三條或更多條傳輸線.

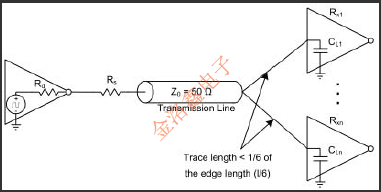

驅(qū)動在跡線末端集中的多個負載

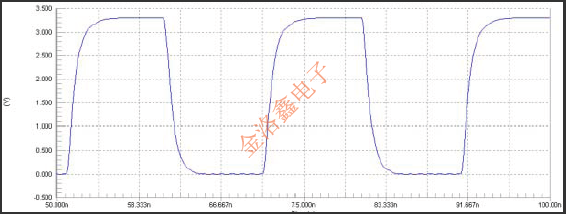

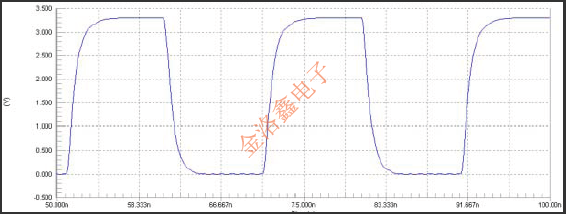

驅(qū)動多個晶振負載的最簡單方案是在傳輸線末端點亮負載(圖3).如果負載可以放置得足夠靠近傳輸線的末端,則可以實現(xiàn),使得將每個負載連接到傳輸線的跡線不長于信號邊緣的有效長度的六分之一.負載必須以”星形”形式連接,如圖3所示.串聯(lián)終端電阻的值的計算方法與單個負載情況相同(公式2). 圖4說明了圖3中針對SiT8208-3.3V石英晶體振蕩器的方案的Altium Designer仿真結果,其中Rs=43Ω,CL=5pF,時鐘接收器數(shù)量-2,短截線長度0.5英寸(~75ps).如果短截線太長,則反射會導致信號完整性問題(見圖5).

圖4:SiT8208的Altium Designer仿真波形(在負載側)驅(qū)動5英寸末端的兩個負載.跟蹤.走線阻抗-60Ω,電源電壓-3.3V,源端電壓-43Ω,負載電容-5pF.

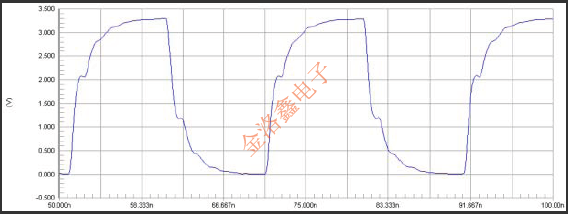

圖5:SiT8208的Altium Designer仿真波形(在負載側)驅(qū)動兩個負載時,驅(qū)動器的走線在2英寸后分成兩個3英寸.每個都連接到負載的部分.阻抗-60Ω,電源電壓-3.3V,源端接-43Ω,負載電容-5pF.

圖4:SiT8208的Altium Designer仿真波形(在負載側)驅(qū)動5英寸末端的兩個負載.跟蹤.走線阻抗-60Ω,電源電壓-3.3V,源端電壓-43Ω,負載電容-5pF.

圖5:SiT8208的Altium Designer仿真波形(在負載側)驅(qū)動兩個負載時,驅(qū)動器的走線在2英寸后分成兩個3英寸.每個都連接到負載的部分.阻抗-60Ω,電源電壓-3.3V,源端接-43Ω,負載電容-5pF.

PCB上的兩個或更多Oscillator可能需要相同頻率的輸入時鐘.使用時鐘驅(qū)動多個負載的一種方法是使用扇出緩沖器,這需要額外的電路板空間和功率.另一種方法是將一個輸出連接到多個負載.將一個輸出連接到多個負載的首選方法是將單個傳輸線路由到盡可能靠近負載,并使用星形連接將負載連接到短路徑,因此負載在路徑末端被認為是集總的.該方法要求負載彼此足夠接近.

如果負載彼此相距太遠而無法使用集總負載配置,那么在某些條件下,可以使用一個輸出來驅(qū)動兩條輸電線路分離負載.這種配置要求輸出驅(qū)動器具有比驅(qū)動單條傳輸線更高的電流驅(qū)動能力,當使用60Ω和更低阻抗的傳輸線時,不建議將其與1.8V版本的SiT1602和表2中列出的其他器件一起使用.在將此配置合并到設計中之前,建議使用IBIS模型運行信號完整性仿真.

某些驅(qū)動程序可能沒有足夠的驅(qū)動能力來處理兩條傳輸線.如果振蕩器輸出和負載之間的距離足夠小,則可以考慮星形拓撲.典型石英晶體振蕩器的輸出驅(qū)動器強度不足以驅(qū)動三條或更多條傳輸線,并且可以在PCB(50-60Ω)上輕松設計走線阻抗.SiTime晶振不建議從單個驅(qū)動器驅(qū)動三條或更多條傳輸線.

驅(qū)動在跡線末端集中的多個負載

驅(qū)動多個晶振負載的最簡單方案是在傳輸線末端點亮負載(圖3).如果負載可以放置得足夠靠近傳輸線的末端,則可以實現(xiàn),使得將每個負載連接到傳輸線的跡線不長于信號邊緣的有效長度的六分之一.負載必須以”星形”形式連接,如圖3所示.串聯(lián)終端電阻的值的計算方法與單個負載情況相同(公式2). 圖4說明了圖3中針對SiT8208-3.3V石英晶體振蕩器的方案的Altium Designer仿真結果,其中Rs=43Ω,CL=5pF,時鐘接收器數(shù)量-2,短截線長度0.5英寸(~75ps).如果短截線太長,則反射會導致信號完整性問題(見圖5).

正在載入評論數(shù)據(jù)...

相關資訊

- [2025-09-03]Greenray格林雷晶振T1254系列具...

- [2025-09-01]壓電執(zhí)行器被用于衛(wèi)星微推進器以...

- [2025-09-01]探索主動阻尼的加速度感測技術用...

- [2025-08-26]使用振蕩器和時鐘發(fā)生器整合頻率...

- [2025-08-26]Vectron維管晶振的國防振蕩器在...

- [2024-03-15]Cardinal晶振常見問題CX5Z-A2B2...

- [2024-03-04]Jauch的40MHz的石英毛坯有多厚?...

- [2023-09-21]Skyworks領先同行的綠色生產(chǎn)標準...

業(yè)務經(jīng)理

業(yè)務經(jīng)理 客服經(jīng)理

客服經(jīng)理