系統(tǒng)頻率源可通過時鐘發(fā)生器與晶振整合優(yōu)劣點

來源:http://www.benpai.com.cn 作者:金洛鑫電子 2019年09月17

典型的系統(tǒng)設(shè)計最初側(cè)重于微控制器(MCU),CPU,存儲器和I/O組件和架構(gòu),稍后將重點介紹如何提供系統(tǒng)所需的各種時鐘.復(fù)雜的系統(tǒng)最終可能需要10個或更多時鐘.考慮到分立諧振器,晶體振蕩器,扇出緩沖器,時鐘發(fā)生器和其他定時器件選項的選擇,提供所有這些頻率的最佳方法是什么?通過將時序需求整合到硅時鐘發(fā)生器組件中,可以降低電路板空間和系統(tǒng)成本.但這種方法總是有意義的,在電路板面積,成本,系統(tǒng)時序裕度,噪聲抗擾度和電磁干擾(EMI)方面的系統(tǒng)權(quán)衡是什么?

典型的系統(tǒng)設(shè)計:

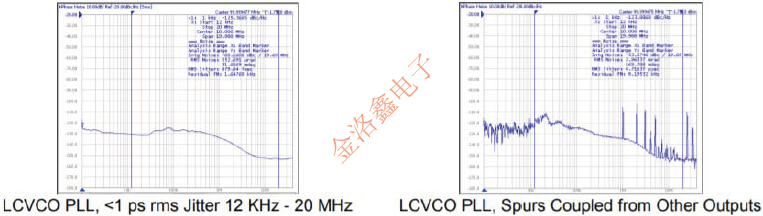

假設(shè)您已完成系統(tǒng)的架構(gòu)并選擇了關(guān)鍵組件.它與現(xiàn)實世界接口,因此至少有一個放大器,A/D或D/A,某種類型的人機接口,MCU和/或DSP,存儲器,無線和/或有線互聯(lián)網(wǎng)連接以及相關(guān)的電源管理(見圖1).模擬的上電和斷電序列,信噪比,計算速度,存儲器帶寬和功耗均符合規(guī)范.您幾乎已準(zhǔn)備好進行電路板布局以模擬布局寄生效應(yīng)并確保它們不會中斷性能.您還計劃遵循布局指南以最大限度地降低EMI,但由于難以建模,您仍然需要克服系統(tǒng)在EMI測試期間通過FCC規(guī)則限制. 系統(tǒng)頻率規(guī)劃:

進入布局之前的最后一步是選擇所有組件的頻率參考.有些器件只有一個需要外部振蕩器的Clock-IN引腳,有些器件可以與外部時鐘或晶振一起工作.一個關(guān)于嘗試在先前設(shè)計中的特定溫度和電壓角調(diào)試石英晶體振蕩器啟動問題的故事.當(dāng)與特定晶體和負(fù)載一起使用時,最終證明晶體振蕩器增益不足.你肯定想避免這個問題!此外,質(zhì)量保證團隊警告晶體的機械不可靠性.您需要計算所需的頻率,總共八個,A/D,D/A,MCU,內(nèi)存,LAN和WLAN組件各一個,DSP/SOC兩個.如果您可以從單個時鐘發(fā)生器生成所有這些頻率并將它們路由到各種組件,則可以節(jié)省大量的面積和組件成本,并通過使用單晶來提高可靠性.但系統(tǒng)還能運作嗎?時鐘發(fā)生器能否提供每個組件所需的頻率和信號質(zhì)量,以及可能出現(xiàn)的其他優(yōu)點或缺點?

如果你曾經(jīng)歷過這種不確定性,那么你并不孤單.每個盡責(zé)的系統(tǒng)設(shè)計師都會在嘗試以最低的總成本(包括元件數(shù)量,面積,可制造性和可靠性)優(yōu)化頻率生成性能時詢問.雖然每個系統(tǒng)都不同,但請考慮以下有用的指導(dǎo)方針來做出決定.

頻率發(fā)生器基礎(chǔ)知識:

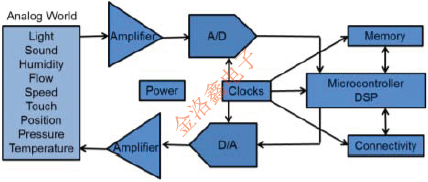

為了理解將頻率源合并到時鐘發(fā)生器中的權(quán)衡,我們需要了解替代源的優(yōu)點和局限性,如圖2所示. 離散諧振器:

分立諧振器被設(shè)計成與半導(dǎo)體增益電路一起工作,該半導(dǎo)體增益電路連接到諧振器的兩個端子.增益電路的輸出最初是其輸入端的放大噪聲.諧振器材料的壓電和物理特性允許振動諧振器用作電子濾波器,將其通帶中的頻率分量傳遞回放大器的輸入端.在環(huán)路增益>1且相位為360度的通帶頻率下,諧振器開始振蕩,在放大器輸出端產(chǎn)生穩(wěn)定的頻率源.

可用的兩種最常見的分立諧振器是陶瓷(通常由鉛-鋯-鈦或PZT)諧振器和石英水晶振子(由二氧化硅或SiO2制成)諧振器.主要區(qū)別在于陶瓷諧振器成本更低且精度更低,初始精度>5000ppm,并且隨溫度和老化而顯著漂移(在商業(yè)應(yīng)用中各約為2000ppm).晶體諧振器更精確,精度<50ppm,包括AT切割晶體的溫度和老化.某些ASIC也使用晶體諧振器,這些ASIC設(shè)計用于改變引腳上的電容,以控制頻率的微小偏差(<+/-150ppm),作為壓控晶體振蕩器(VCXO).

離散諧振器的主要缺點之一是確保增益電路,石英晶振和電路板布局(均來自不同制造商)正確匹配所需的工作量和開發(fā)時間.該分析包括驗證可靠的啟動和溫度,過程和電壓的準(zhǔn)確性.此外,分析需要確保晶體不會過度驅(qū)動,這會加速老化.此外,外部信號的較低幅度和正弦波形導(dǎo)致信號邊緣較慢,這使得分立諧振器對外部噪聲更敏感.分立諧振器的優(yōu)點包括出色的近端相位噪聲,諧振頻率的KHz內(nèi)的噪聲和低功耗.

離散振蕩器:

分立振蕩器將上述半導(dǎo)體放大器與諧振器組合在同一封裝中.晶體諧振器是最常見的諧振器類型,盡管有時使用表面聲波(SAW)諧振器和最近的微機電系統(tǒng)(MEMS)諧振器.SAW諧振器工作在更高的頻率(>400MHz),MEMS諧振器提供類似于晶體的性能,具有更小和更耐沖擊的優(yōu)點.

分立振蕩器的一個關(guān)鍵優(yōu)勢是放大器,諧振器和連接電容可以在工廠匹配,以確保可靠的啟動和頻率精度,與電路板布局無關(guān).當(dāng)然,與分立諧振器相比,這會增加元件成本,面積和功耗.由于大多數(shù)振蕩器僅產(chǎn)生一個頻率,因此在需要時將頻率合并到一個或兩個時鐘發(fā)生器中通常可以更好地服務(wù)于需要多個頻率的系統(tǒng).

時鐘發(fā)生器:

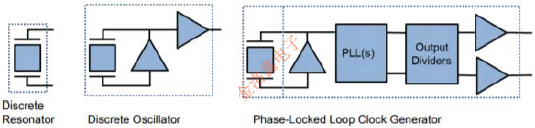

時鐘發(fā)生器或有時稱為頻率發(fā)生器的振蕩器將振蕩器與一個或多個鎖相環(huán)(PLL),輸出分頻器和輸出緩沖器組合在一起.在大多數(shù)情況下,諧振器是外部的,但業(yè)界有一種趨勢,即將諧振器包括在時鐘發(fā)生器封裝內(nèi),以消除上面概述的分立諧振器的缺點.然而,即使諧振器是外部的,由于時鐘發(fā)生器僅需要一個參考來產(chǎn)生所有其他頻率,因此大大減少了匹配諧振器,放大器和電路板布局所需的工作量.此外,最小化分立諧振器的數(shù)量將提高系統(tǒng)的堅固性和可靠性.

將頻率合并到時鐘發(fā)生器中的優(yōu)點很多.除了上面提到的減少的晶振匹配工作和改進的可靠性之外,高級時鐘發(fā)生器通常還提供多種有益于系統(tǒng)性能的功能.輸出頻率可以實時更改,這在系統(tǒng)必須適應(yīng)全球各種標(biāo)準(zhǔn)(例如PAL與NTSC),以適應(yīng)最終用戶的系統(tǒng)變化(例如連接不同的視頻監(jiān)視器)或適應(yīng)用于確保供應(yīng)的BOM更改(例如,支持來自兩個具有不同采樣率的供應(yīng)商的音頻DAC).在系統(tǒng)驗證或生產(chǎn)測試期間,系統(tǒng)時鐘頻率也可以稍微變化以確保足夠的時序裕度,并且可以采用擴頻時鐘來降低EMI抑制的成本.

有許多不同類型的時鐘發(fā)生器,每個都針對不同的性能和成本目標(biāo)進行了優(yōu)化.這些差異包括:

•基于環(huán)形振蕩器與LC振蕩器的PLL.(環(huán)形振蕩器PLL通常提供更低的成本,功耗和性能,而LC振蕩器PLL以更高的成本和功耗為代價提供更高的性能.)

•單端CMOS輸出,用于最小功率與差分晶振輸出,如LVPECL,LVDS和HCSL,可以降低耦合噪聲,但代價是功耗更高.

•在晶體振蕩器上加入自動增益控制,以最大限度地提高啟動增益,然后降低增益,最大限度地降低晶體功耗和相關(guān)老化,而低成本的逆變器振蕩器則帶有內(nèi)部或外部功率限制電阻.

•串行通信接口與預(yù)編程頻率和引腳可選功能的可用性.

•較小封裝中的輸出數(shù)量較少,較大封裝中的輸出數(shù)量較多.

•允許混合電壓電源驅(qū)動不同的輸出電壓電壓而不是單電源電壓.

瀏覽各種可用的時鐘發(fā)生器并嘗試將它們與您的系統(tǒng)要求相匹配可能是一項艱巨的任務(wù).因此,強烈建議與時鐘供應(yīng)商合作,該供應(yīng)商提供大量可用時鐘發(fā)生器,以確保最佳解決方案.只有幾家半導(dǎo)體公司提供全面的時鐘發(fā)生器產(chǎn)品組合,SiliconLabs就是其中之一.

為您的系統(tǒng)選擇合適的頻率源:

以下決策樹將有助于縮小頻率源選擇范圍,并制定最佳計劃,以最大限度地減少系統(tǒng)中的頻率源組件和相關(guān)成本.

標(biāo)準(zhǔn)1:如果系統(tǒng)只需要一個或兩個<50MHz的頻率,則離散晶體或是振蕩器成本最低的解決方案.如果頻率>50MHz,或者需要多個副本或頻率的特殊控制,那么扇出緩沖器或時鐘發(fā)生器將提供更低成本的解決方案.特殊功能包括在系統(tǒng)運行或測試期間改變頻率以及用于降低EMI的擴頻技術(shù).

標(biāo)準(zhǔn)2:如果系統(tǒng)中有組件可以提取離散晶體的頻率,那么離散晶體是您唯一的選擇.確保使用ASIC供應(yīng)商推薦的產(chǎn)品或與其指定的詳細(xì)晶體參數(shù)匹配的產(chǎn)品.

標(biāo)準(zhǔn)3:如果系統(tǒng)中的組件需要在溫度和電壓范圍內(nèi)具有極其精確的時鐘(<20ppm),則需要外部振蕩器,如溫度控制晶體振蕩器(TCXO).如果您的系統(tǒng)除了一個高精度頻率外還需要頻率,TCXO通常可以用作時鐘發(fā)生器的參考,以節(jié)省成本.必須注意使溫補晶振信號電平與時鐘發(fā)生器輸入電平相匹配,并將耦合噪聲降至主TCXO信號路徑.

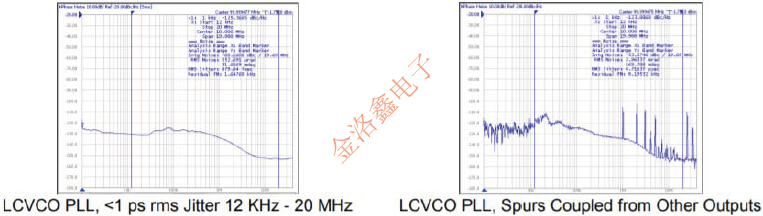

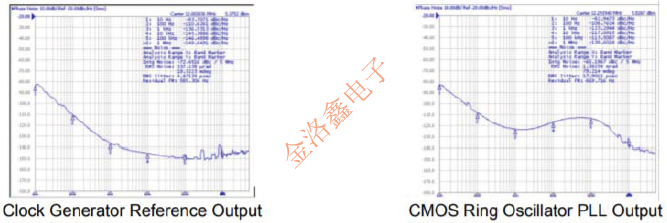

標(biāo)準(zhǔn)4:需要具有特定相位噪聲要求的頻率(通常用于無線通信參考)的組件通常需要來自晶體振蕩器或基于LC的頻率發(fā)生器,如圖3所示.由于成本較低的基于環(huán)的時鐘發(fā)生器通常使用石英晶振作為參考,大多數(shù)時鐘發(fā)生器直接輸出該頻率(不通過PLL)以提供低相位噪聲信號.但是,如果同一時鐘發(fā)生器正在生成具有不同頻率的多個輸出,請務(wù)必檢查參考頻率輸出頻譜中的雜散內(nèi)容,以確保它不會干擾或混淆相鄰的無線信道.支線位置將根據(jù)生成頻率的組合而改變.如果雜散電平或位置與應(yīng)用程序不兼容,將一些時鐘生成移動到第二個時鐘發(fā)生器可能會解決問題.否則,需要分立諧振器或分立振蕩器. 標(biāo)準(zhǔn)5:需要具有嚴(yán)格“rms抖動”要求的參考頻率的Oscillator也可由時鐘發(fā)生器提供.這是高速數(shù)字通信系統(tǒng)的通用規(guī)范.抖動是時鐘邊沿相對于“完美”時鐘信號的不確定性或誤差,均方根相位抖動是特定頻帶上相位噪聲的積分(見圖4).一種非常常見的rms抖動規(guī)范源于Sonet數(shù)據(jù)傳輸應(yīng)用,并且在12KHz至20MHz頻帶上指定為<1psrms.由于該標(biāo)準(zhǔn)已經(jīng)存在了幾十年,許多半導(dǎo)體元件將其指定為默認(rèn)的抖動限制,而不實際計算真正的系統(tǒng)抖動要求.

圖4.使能和不使用附加頻率輸出的LCVCOPLL

利用多個頻率生成源,可以在保持優(yōu)異系統(tǒng)性能的同時優(yōu)化系統(tǒng)時鐘要求,降低總體成本.在一些情況下,僅需要無源諧振器,而在系統(tǒng)中,尤其是那些需要兩個或更多頻率的石英晶振,無源諧振器最好由硅定時器件代替,例如時鐘發(fā)生器和扇出緩沖器.除了降低頻率生成和EMI抑制成本之外,硅頻率發(fā)生器還提供了額外的BOM固結(jié),系統(tǒng)可配置性和測試能力.

典型的系統(tǒng)設(shè)計:

假設(shè)您已完成系統(tǒng)的架構(gòu)并選擇了關(guān)鍵組件.它與現(xiàn)實世界接口,因此至少有一個放大器,A/D或D/A,某種類型的人機接口,MCU和/或DSP,存儲器,無線和/或有線互聯(lián)網(wǎng)連接以及相關(guān)的電源管理(見圖1).模擬的上電和斷電序列,信噪比,計算速度,存儲器帶寬和功耗均符合規(guī)范.您幾乎已準(zhǔn)備好進行電路板布局以模擬布局寄生效應(yīng)并確保它們不會中斷性能.您還計劃遵循布局指南以最大限度地降低EMI,但由于難以建模,您仍然需要克服系統(tǒng)在EMI測試期間通過FCC規(guī)則限制. 系統(tǒng)頻率規(guī)劃:

進入布局之前的最后一步是選擇所有組件的頻率參考.有些器件只有一個需要外部振蕩器的Clock-IN引腳,有些器件可以與外部時鐘或晶振一起工作.一個關(guān)于嘗試在先前設(shè)計中的特定溫度和電壓角調(diào)試石英晶體振蕩器啟動問題的故事.當(dāng)與特定晶體和負(fù)載一起使用時,最終證明晶體振蕩器增益不足.你肯定想避免這個問題!此外,質(zhì)量保證團隊警告晶體的機械不可靠性.您需要計算所需的頻率,總共八個,A/D,D/A,MCU,內(nèi)存,LAN和WLAN組件各一個,DSP/SOC兩個.如果您可以從單個時鐘發(fā)生器生成所有這些頻率并將它們路由到各種組件,則可以節(jié)省大量的面積和組件成本,并通過使用單晶來提高可靠性.但系統(tǒng)還能運作嗎?時鐘發(fā)生器能否提供每個組件所需的頻率和信號質(zhì)量,以及可能出現(xiàn)的其他優(yōu)點或缺點?

如果你曾經(jīng)歷過這種不確定性,那么你并不孤單.每個盡責(zé)的系統(tǒng)設(shè)計師都會在嘗試以最低的總成本(包括元件數(shù)量,面積,可制造性和可靠性)優(yōu)化頻率生成性能時詢問.雖然每個系統(tǒng)都不同,但請考慮以下有用的指導(dǎo)方針來做出決定.

頻率發(fā)生器基礎(chǔ)知識:

為了理解將頻率源合并到時鐘發(fā)生器中的權(quán)衡,我們需要了解替代源的優(yōu)點和局限性,如圖2所示. 離散諧振器:

分立諧振器被設(shè)計成與半導(dǎo)體增益電路一起工作,該半導(dǎo)體增益電路連接到諧振器的兩個端子.增益電路的輸出最初是其輸入端的放大噪聲.諧振器材料的壓電和物理特性允許振動諧振器用作電子濾波器,將其通帶中的頻率分量傳遞回放大器的輸入端.在環(huán)路增益>1且相位為360度的通帶頻率下,諧振器開始振蕩,在放大器輸出端產(chǎn)生穩(wěn)定的頻率源.

可用的兩種最常見的分立諧振器是陶瓷(通常由鉛-鋯-鈦或PZT)諧振器和石英水晶振子(由二氧化硅或SiO2制成)諧振器.主要區(qū)別在于陶瓷諧振器成本更低且精度更低,初始精度>5000ppm,并且隨溫度和老化而顯著漂移(在商業(yè)應(yīng)用中各約為2000ppm).晶體諧振器更精確,精度<50ppm,包括AT切割晶體的溫度和老化.某些ASIC也使用晶體諧振器,這些ASIC設(shè)計用于改變引腳上的電容,以控制頻率的微小偏差(<+/-150ppm),作為壓控晶體振蕩器(VCXO).

離散諧振器的主要缺點之一是確保增益電路,石英晶振和電路板布局(均來自不同制造商)正確匹配所需的工作量和開發(fā)時間.該分析包括驗證可靠的啟動和溫度,過程和電壓的準(zhǔn)確性.此外,分析需要確保晶體不會過度驅(qū)動,這會加速老化.此外,外部信號的較低幅度和正弦波形導(dǎo)致信號邊緣較慢,這使得分立諧振器對外部噪聲更敏感.分立諧振器的優(yōu)點包括出色的近端相位噪聲,諧振頻率的KHz內(nèi)的噪聲和低功耗.

離散振蕩器:

分立振蕩器將上述半導(dǎo)體放大器與諧振器組合在同一封裝中.晶體諧振器是最常見的諧振器類型,盡管有時使用表面聲波(SAW)諧振器和最近的微機電系統(tǒng)(MEMS)諧振器.SAW諧振器工作在更高的頻率(>400MHz),MEMS諧振器提供類似于晶體的性能,具有更小和更耐沖擊的優(yōu)點.

分立振蕩器的一個關(guān)鍵優(yōu)勢是放大器,諧振器和連接電容可以在工廠匹配,以確保可靠的啟動和頻率精度,與電路板布局無關(guān).當(dāng)然,與分立諧振器相比,這會增加元件成本,面積和功耗.由于大多數(shù)振蕩器僅產(chǎn)生一個頻率,因此在需要時將頻率合并到一個或兩個時鐘發(fā)生器中通常可以更好地服務(wù)于需要多個頻率的系統(tǒng).

時鐘發(fā)生器:

時鐘發(fā)生器或有時稱為頻率發(fā)生器的振蕩器將振蕩器與一個或多個鎖相環(huán)(PLL),輸出分頻器和輸出緩沖器組合在一起.在大多數(shù)情況下,諧振器是外部的,但業(yè)界有一種趨勢,即將諧振器包括在時鐘發(fā)生器封裝內(nèi),以消除上面概述的分立諧振器的缺點.然而,即使諧振器是外部的,由于時鐘發(fā)生器僅需要一個參考來產(chǎn)生所有其他頻率,因此大大減少了匹配諧振器,放大器和電路板布局所需的工作量.此外,最小化分立諧振器的數(shù)量將提高系統(tǒng)的堅固性和可靠性.

將頻率合并到時鐘發(fā)生器中的優(yōu)點很多.除了上面提到的減少的晶振匹配工作和改進的可靠性之外,高級時鐘發(fā)生器通常還提供多種有益于系統(tǒng)性能的功能.輸出頻率可以實時更改,這在系統(tǒng)必須適應(yīng)全球各種標(biāo)準(zhǔn)(例如PAL與NTSC),以適應(yīng)最終用戶的系統(tǒng)變化(例如連接不同的視頻監(jiān)視器)或適應(yīng)用于確保供應(yīng)的BOM更改(例如,支持來自兩個具有不同采樣率的供應(yīng)商的音頻DAC).在系統(tǒng)驗證或生產(chǎn)測試期間,系統(tǒng)時鐘頻率也可以稍微變化以確保足夠的時序裕度,并且可以采用擴頻時鐘來降低EMI抑制的成本.

有許多不同類型的時鐘發(fā)生器,每個都針對不同的性能和成本目標(biāo)進行了優(yōu)化.這些差異包括:

•基于環(huán)形振蕩器與LC振蕩器的PLL.(環(huán)形振蕩器PLL通常提供更低的成本,功耗和性能,而LC振蕩器PLL以更高的成本和功耗為代價提供更高的性能.)

•單端CMOS輸出,用于最小功率與差分晶振輸出,如LVPECL,LVDS和HCSL,可以降低耦合噪聲,但代價是功耗更高.

•在晶體振蕩器上加入自動增益控制,以最大限度地提高啟動增益,然后降低增益,最大限度地降低晶體功耗和相關(guān)老化,而低成本的逆變器振蕩器則帶有內(nèi)部或外部功率限制電阻.

•串行通信接口與預(yù)編程頻率和引腳可選功能的可用性.

•較小封裝中的輸出數(shù)量較少,較大封裝中的輸出數(shù)量較多.

•允許混合電壓電源驅(qū)動不同的輸出電壓電壓而不是單電源電壓.

瀏覽各種可用的時鐘發(fā)生器并嘗試將它們與您的系統(tǒng)要求相匹配可能是一項艱巨的任務(wù).因此,強烈建議與時鐘供應(yīng)商合作,該供應(yīng)商提供大量可用時鐘發(fā)生器,以確保最佳解決方案.只有幾家半導(dǎo)體公司提供全面的時鐘發(fā)生器產(chǎn)品組合,SiliconLabs就是其中之一.

為您的系統(tǒng)選擇合適的頻率源:

以下決策樹將有助于縮小頻率源選擇范圍,并制定最佳計劃,以最大限度地減少系統(tǒng)中的頻率源組件和相關(guān)成本.

標(biāo)準(zhǔn)1:如果系統(tǒng)只需要一個或兩個<50MHz的頻率,則離散晶體或是振蕩器成本最低的解決方案.如果頻率>50MHz,或者需要多個副本或頻率的特殊控制,那么扇出緩沖器或時鐘發(fā)生器將提供更低成本的解決方案.特殊功能包括在系統(tǒng)運行或測試期間改變頻率以及用于降低EMI的擴頻技術(shù).

標(biāo)準(zhǔn)2:如果系統(tǒng)中有組件可以提取離散晶體的頻率,那么離散晶體是您唯一的選擇.確保使用ASIC供應(yīng)商推薦的產(chǎn)品或與其指定的詳細(xì)晶體參數(shù)匹配的產(chǎn)品.

標(biāo)準(zhǔn)3:如果系統(tǒng)中的組件需要在溫度和電壓范圍內(nèi)具有極其精確的時鐘(<20ppm),則需要外部振蕩器,如溫度控制晶體振蕩器(TCXO).如果您的系統(tǒng)除了一個高精度頻率外還需要頻率,TCXO通常可以用作時鐘發(fā)生器的參考,以節(jié)省成本.必須注意使溫補晶振信號電平與時鐘發(fā)生器輸入電平相匹配,并將耦合噪聲降至主TCXO信號路徑.

標(biāo)準(zhǔn)4:需要具有特定相位噪聲要求的頻率(通常用于無線通信參考)的組件通常需要來自晶體振蕩器或基于LC的頻率發(fā)生器,如圖3所示.由于成本較低的基于環(huán)的時鐘發(fā)生器通常使用石英晶振作為參考,大多數(shù)時鐘發(fā)生器直接輸出該頻率(不通過PLL)以提供低相位噪聲信號.但是,如果同一時鐘發(fā)生器正在生成具有不同頻率的多個輸出,請務(wù)必檢查參考頻率輸出頻譜中的雜散內(nèi)容,以確保它不會干擾或混淆相鄰的無線信道.支線位置將根據(jù)生成頻率的組合而改變.如果雜散電平或位置與應(yīng)用程序不兼容,將一些時鐘生成移動到第二個時鐘發(fā)生器可能會解決問題.否則,需要分立諧振器或分立振蕩器. 標(biāo)準(zhǔn)5:需要具有嚴(yán)格“rms抖動”要求的參考頻率的Oscillator也可由時鐘發(fā)生器提供.這是高速數(shù)字通信系統(tǒng)的通用規(guī)范.抖動是時鐘邊沿相對于“完美”時鐘信號的不確定性或誤差,均方根相位抖動是特定頻帶上相位噪聲的積分(見圖4).一種非常常見的rms抖動規(guī)范源于Sonet數(shù)據(jù)傳輸應(yīng)用,并且在12KHz至20MHz頻帶上指定為<1psrms.由于該標(biāo)準(zhǔn)已經(jīng)存在了幾十年,許多半導(dǎo)體元件將其指定為默認(rèn)的抖動限制,而不實際計算真正的系統(tǒng)抖動要求.

圖4.使能和不使用附加頻率輸出的LCVCOPLL

表1總結(jié)了各種頻率源的優(yōu)缺點.

表1.頻率源的優(yōu)點和局限

表1.頻率源的優(yōu)點和局限

| 頻率源和應(yīng)用 | 優(yōu)勢 | 限制 |

|

陶瓷諧振器 低精度數(shù)字時鐘 |

成本低(除非需要很多) |

精度低,5000-20,000ppm 高溫變化,+/-3000ppm 固定頻率,<10MHz |

|

水晶諧振器 中等精度數(shù)字時鐘 射頻參考 |

需要1或2時的低成本 低電量 一些SoC需要 集成的VCXO |

努力與放大器匹配 布局敏感準(zhǔn)確,啟動 固定頻率,<50MHz 外部噪音敏感 對沖擊敏感 |

|

晶體振蕩器 高精度數(shù)字時鐘 射頻參考 |

可靠的啟動 準(zhǔn)確性對布局不敏感 單頻(無串?dāng)_) |

如果需要>1則成本更高 更高功率>3mA 如果需要>1,則板面積 單頻復(fù)制 >100MHz時價格昂貴 |

|

扇出緩沖區(qū) 同一頻率的多個副本 |

多頻復(fù)制 級別翻譯 同步輸出 |

如果頻率不同,則需要輸入頻率源串?dāng)_ |

|

時鐘發(fā)生器,CMOS環(huán)形PLL 所有數(shù)字時鐘 需要>2個頻率的系統(tǒng), >50MHz,可選擇或傳播 頻率 >50ps最大抖動 |

>2頻率的最低成本 可靠性(更少的晶體) 可選頻率 最小面積和組件數(shù) >50MHz頻率 擴頻用于降低EMI 多頻復(fù)制 |

如果多次發(fā)生頻率則會產(chǎn)生串?dāng)_ |

|

時鐘發(fā)生器,LCVCOPLL 需要>2個頻率的系統(tǒng), >100MHz,可選頻率 高速收發(fā)器, 射頻參考或采樣 <1psrms抖動 |

>2頻率的中等成本 可靠性(更少的晶體) 可選頻率 最小面積和組件數(shù) >50MHz頻率 多頻復(fù)制 |

更高的功率如果存在多個頻率,則會產(chǎn)生串?dāng)_ |

正在載入評論數(shù)據(jù)...

相關(guān)資訊

- [2025-08-29]CTS致力于成為技術(shù)的前沿提供創(chuàng)...

- [2025-08-29]Diodes宣布推出一款智能48通道L...

- [2025-08-25]Rakon瑞康為什么應(yīng)該放棄標(biāo)準(zhǔn)CO...

- [2025-08-25]Transko特蘭斯科推出了結(jié)合MEMS...

- [2025-08-23]SiT5503超精密溫度補償晶體振蕩...

- [2025-08-23]探索SiTime專為導(dǎo)航航空航天和國...

- [2024-04-11]CTECH濾波器型號數(shù)據(jù)列表CLB75P...

- [2024-03-18]Statek晶振產(chǎn)品應(yīng)用CX20SCSM1-1...

業(yè)務(wù)經(jīng)理

業(yè)務(wù)經(jīng)理 客服經(jīng)理

客服經(jīng)理